Wayne State University

Wayne State University Dissertations

1-1-2014

# Flexible Mems: A Novel Technology To Fabricate Flexible Sensors And Electronics

Hongen Tu Wayne State University,

Follow this and additional works at: http://digitalcommons.wayne.edu/oa\_dissertations Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Tu, Hongen, "Flexible Mems: A Novel Technology To Fabricate Flexible Sensors And Electronics" (2014). *Wayne State University Dissertations*. Paper 1058.

This Open Access Dissertation is brought to you for free and open access by DigitalCommons@WayneState. It has been accepted for inclusion in Wayne State University Dissertations by an authorized administrator of DigitalCommons@WayneState.

#### FLEXIBLE MEMS: A NOVEL TECHNOLOGY TO FABRICATE FLEXIBLE SENSORS AND ELECTRONICS

by

#### HONGEN TU

#### DISSERTATON

Submitted to the Graduate School

of Wayne State University,

Detroit, Michigan

in partial fulfillment of the requirements

for the degree of

#### **DOCTOR OF PHILOSOPHY**

2014

MAJOR: ELECTRICAL ENGINEERING

Approved by:

Adviser

Date

### © COPYRIGHT BY

#### HONGEN TU

2014

All Rights Reserved

# ACKNOWLEDGMENTS

I would like to express my sincere appreciation and thanks to my advisor Professor Yong Xu who has been a tremendous mentor for me throughout my PhD career. I would like to thank him for providing ingenious ideas and great insight on my research projects and for allowing me to grow as a research scientist. I would also like to thank my committee members, Dr. Amar S. Basu, Dr. Ming-Cheng Cheng and Dr. Jinsheng Zhang for serving as my committee members and for their support, comments and suggestions.

I would also like to thank all of the helpful staff at nFab including Bill Funk and Dan Durisin for providing critical technical support during my cleanroom fabrication. I would like to acknowledge my fellow lab mates Dr. Yuefa Li and Dr.Qinglong Zheng for guiding me through all of the important microfabrication techniques. My appreciation also goes to Yating Hu, Jessin John and Eric Kim, and everyone that has been there to support me for all of my research activities.

A special thanks goes to my family. Words cannot express how grateful I am to my parents Maozi Tu/YongZhen Gao and my sister Huan Tu for all of their love, sacrifices and unconditional support towards my career. My special thanks also go to my wife Mengying Liu for being here with me every step of the way.

Finally, I would like to thank Wayne State University for providing me with wonderful resources including a variety of classes and state of the art facilities to support all of my research activities.

# **TABLE OF CONTENTS**

| Acknowledgmentsii                                                                        |

|------------------------------------------------------------------------------------------|

| List of Figuresvi                                                                        |

| Chapter 1. Introduction1                                                                 |

| 1.1 Motivation1                                                                          |

| 1.2 Review of flexible electronics                                                       |

| 1.3 Review of the key material and processes                                             |

| 1.3.1 Parylene C chemical vapor deposition10                                             |

| 1.3.2 XeF <sub>2</sub> isotropic silicon etching13                                       |

| 1.3.3 Deep reactive-ion etching16                                                        |

| 1.4 Dissertation Organization                                                            |

| Chapter 2. Parylene microtube arrays                                                     |

| 2.1 Introduction23                                                                       |

| 2.2 Design and fabrication                                                               |

| 2.3 Results and discussion                                                               |

| 2.3.1 Fabricated device                                                                  |

| 2.3.2. Fluidic injection test                                                            |

| 2.3.3. Preliminary in-vitro retina test                                                  |

| 2.4 Summary                                                                              |

| Chapter 3. Hybrid silicon-polymer platform for self-locking and self-deploying origami36 |

| 3.1 Introduction                                                                         |

| 3.2 Design and fabrication                                                               |

| 3.3 Device testing and characterization                                                            |

|----------------------------------------------------------------------------------------------------|

| 3.4 Summery                                                                                        |

| Chapter 4. SOI-CMOS compatible technology to make flexible electronics                             |

| 4.1 Introduction46                                                                                 |

| 4.2 Design and fabrication                                                                         |

| 4.2.1 Fabricated MOSFETs52                                                                         |

| 4.2.2 Fabricated Strain Gauges55                                                                   |

| 4.3 Summary                                                                                        |

| Chapter 5. A parylene smart tube technology compatible with high-temperature solid-state materials |

| 5.1 Introduction60                                                                                 |

| 5.2 Design and fabrication61                                                                       |

| 5.3 Results and discussion63                                                                       |

| 5.4 Summary70                                                                                      |

| Chapter 6. Additional applications and future work71                                               |

| 6.1 Smart yarn devices71                                                                           |

| 6.1.1 Introduction71                                                                               |

| 6.1.2 Fabrication72                                                                                |

| 6.1.3 Results and discussion74                                                                     |

| 6.1.3.1 Bending test of the integrated strain gauge78                                              |

| 6.1.3.2 Electrical characteristics of MOSFET80                                                     |

| 6.1.3.3 Implementation of the smart yard device to blood pulse measurement                         |

| 6.1.4 Conclusion                                    | .82 |

|-----------------------------------------------------|-----|

| 6.2. Micro PH sensors                               | .83 |

| 6.2.1. Introduction                                 | .83 |

| 6.2.2. Working principle of a conventional pH meter | .84 |

| 6.2.3. Design and fabrication                       | .86 |

| 6.2.4. Device testing and characterization          | .88 |

| 6.2.5 Summary                                       | .91 |

| 6.3 Conclusion and future work                      | .92 |

| References                                          | .94 |

| Abstract                                            | 105 |

| Autobiographical Statement                          | 108 |

v

# **LIST OF FIGURES**

| <b>Figure 1.1</b> Flexible PCB inside Olympus Stylus camera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Figure 1.2</b> (a) Photographs of a 12.5-um-thick polyimide substrate with functional organic TFTs and organic complementary circuits[17]. The array has an area of 75x75mm <sup>2</sup> . (b), Schematic cross-section of the TFTs                                                                                                                                                                                                                                                                                                         |

| <b>Figure 1.3</b> (a) picture of a folded skin; (b) Simplified process flow of the flexible skin with integrated strain gauges                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <ul> <li>Figure 1.4 (a) Optical images of the selective transfer of µs-Si onto a PU/PET sheet;</li> <li>(b)Schematic illustration of selective transfer of us-Si onto PET plastic substrate using patterned hard PDMS [13]</li></ul>                                                                                                                                                                                                                                                                                                           |

| Figure 1.5 A common step flow of chemical vapor deposition of parylene                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 1.6 Schematic illustration of conformal CVD coating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 1.7 Schematic of XeF <sub>2</sub> isotropic silicon etching apparatus                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <b>Figure 1.8</b> Under cut observed after few loops of XeF <sub>2</sub> Silicon etching. A circular hole is opened in parylene C layer which functioned as a masking layer                                                                                                                                                                                                                                                                                                                                                                    |

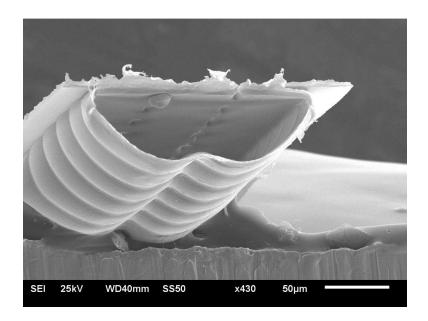

| Figure 1.9 A simple demonstration of deep reactive ion etched trench using Bosch process. 17                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

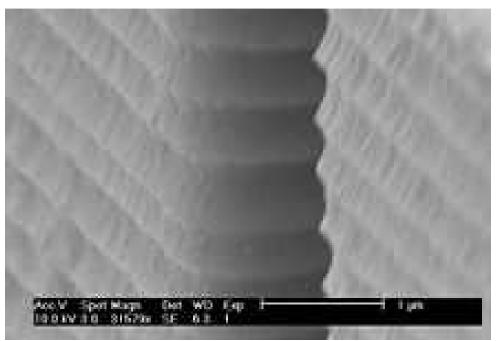

| Figure 1.10 scallops of a silicon structure created using the Bosch process                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <b>Figure 1.11</b> Different DRIE recipies to create different slope angles[31]. (a) Trench with a positive slope. (b) Trench with a negative slope                                                                                                                                                                                                                                                                                                                                                                                            |

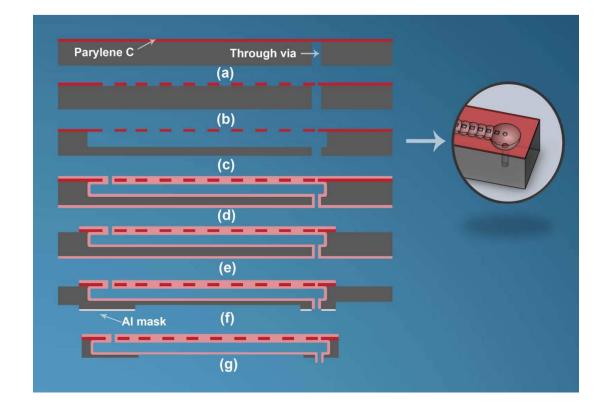

| <b>Figure 2.1</b> The fabrication process of the microneedles with integrated microchannels(a) deposit a parylene C layer; etch through-Silicon vias from the backside of the wafer using DRIE; (b) pattern the parylene layer; (c) etch the silicon substrate using XeF <sub>2</sub> ; (d) coat a thick parylene layer to seal the channel; (e) pattern the frontside parylene; (f) DRIE from the backside of the wafer using Al mask; (g) remove Al mask and continue DRIE to release parylene cable. Out-of-plane microneedles also emerged |

| Figure 2.2 (a) A Delyimide Tubing counled microneedle device with 1.5 cm long flevible                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

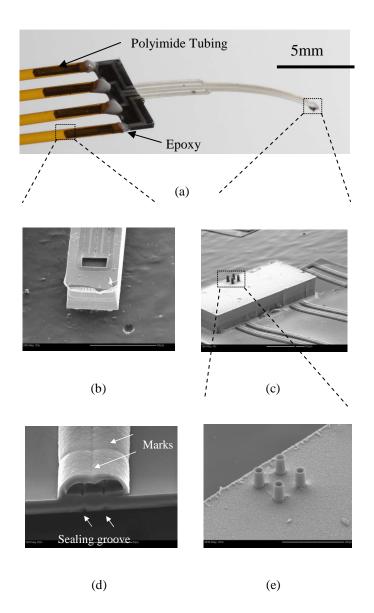

Figure 2.2 (a) A Polyimide Tubing coupled microneedle device with 1.5 cm long flexible parylene cable. Epoxy is used to seal the coupling interface; (b) SEM image of the microchannel inlet port on one coupling beam; (c) SEM image of the small Silicon island on the tip of the parylene cable; (d) cross-sectional view of a

vi

المتسارك للاستشارات

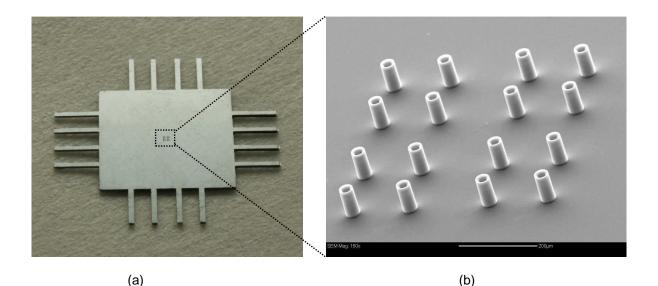

| Figure 2.3 | (a) Photograph of a rigid microneedle device. The device carries 16 slender<br>beams, each of which contains one microchannel inlet. (b) SEM image of the<br>4x4 microneedle array located in the center of the chip, which can be<br>addressable by 16 microchannels                                                                                                                                                                                                    |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.4 | (a) SEM image of the pure parylene device by dissolving away Silicon. (b)<br>Magnified SEM image of the connection between out-of-plane microneedles<br>and in-plane channels                                                                                                                                                                                                                                                                                            |

| Figure 2.5 | 6 (a) Optical micrograph showing a water droplet emerging from one microneedle. (b) The measured relationship between the applied pressure and flow rate. The inset is a fluorescent image of the microchannel and donut structure at the bottom of the microneedle (the channel was filled with fluorescent solution)                                                                                                                                                   |

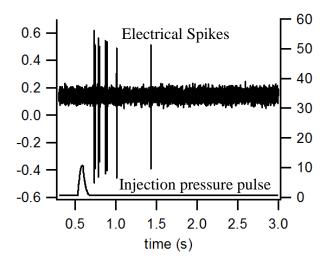

| Figure 2.6 | Neurotransmitter ejection pressure pulse and the resulting neural spikes 33                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 3.1 | Schematic of the silicon island origami with a parylene balloon crease for self-locking and self-deploying functions                                                                                                                                                                                                                                                                                                                                                     |

| Figure 3.2 | Simplified fabrication process of the Origami device                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 3.3 | (a) Front side micrograph of an actual fabricated micro hinge structure with three individual Paraffin wax filled parylene balloon hinge; (b) micrograph of the metal heater integrated on the parylene balloon                                                                                                                                                                                                                                                          |

| Figure 3.4 | (a) Front side and (b) backside SEM images of a parylene balloon cut to show its cross section. The inset shows the enlarged view of the balloon41                                                                                                                                                                                                                                                                                                                       |

| Figure 3.5 | Stiffness measurements of the parylene balloon with solid and melted wax43                                                                                                                                                                                                                                                                                                                                                                                               |

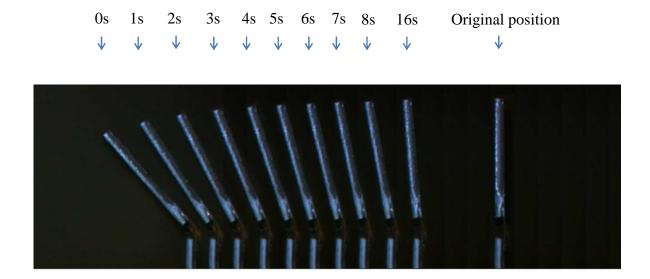

| Figure 3.6 | Snap shots of the device during a self-deploying process after the heater was turned on at 0 second                                                                                                                                                                                                                                                                                                                                                                      |

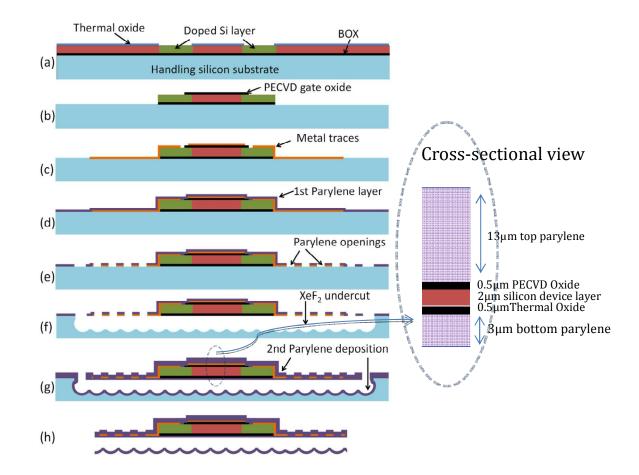

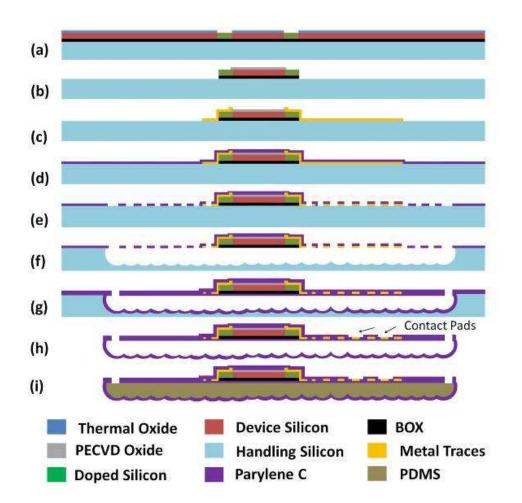

| Figure 4.1 | Simplified process flow: (a) Boron diffusion; (b) patterning the device layer<br>and removing the exposed BOX layer; (c) Al deposition and patterning to form<br>traces and pads; (d) 1st 3 $\mu$ m parylene deposition; (e) patterning the parylene<br>openings and etching away underneath metal traces; (f) XeF <sub>2</sub> etching to release<br>the devices; (g) 2nd 10 $\mu$ m parylene deposition; (h) patterning the parylene<br>layer and releasing the device |

vii

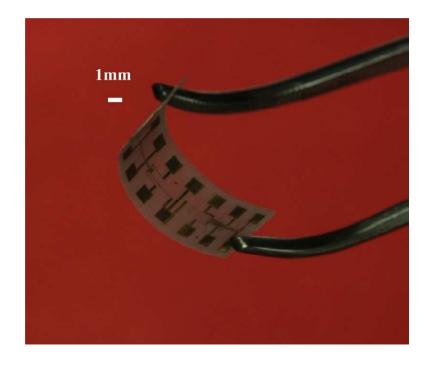

| Figure 4.2 A bent flexible device held by a pair of tweezers                                                                                                                                                                                                                                                                                                                                                                                                           |

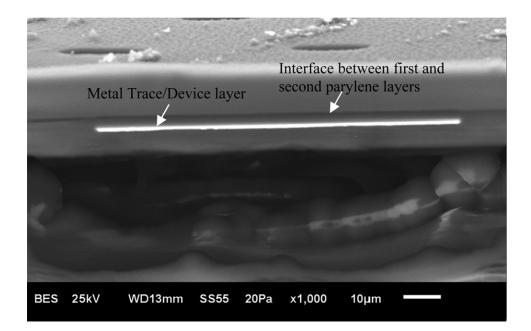

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.3 Cross sectional SEM image of the flexible device                                                                                                                                                                                                                                                                                                                                                                                                            |

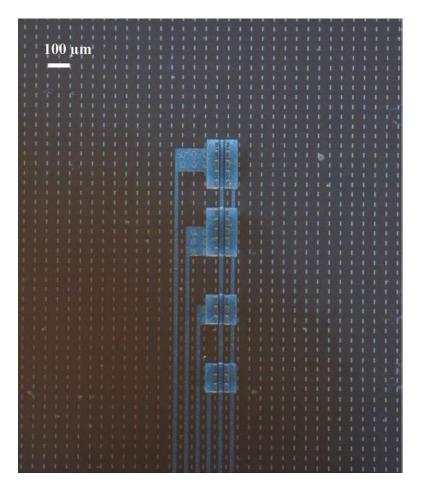

| Figure 4.4 Optical micrograph of four MOSFETs with different channel widths52                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 4.5 SEM image of a MOSFET integrated on the flexible substrate                                                                                                                                                                                                                                                                                                                                                                                                  |

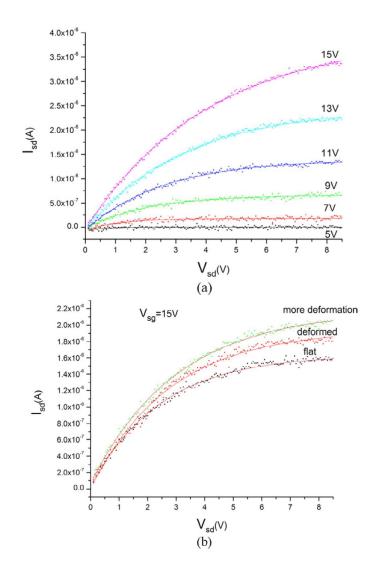

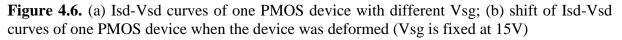

| <b>Figure 4.6</b> (a) Isd-Vsd curves of one PMOS device with different Vsg; (b) shift of Isd-Vsd curves of one PMOS device when the device was deformed (Vsg is fixed at 15V)                                                                                                                                                                                                                                                                                          |

| Figure 4.7 Optical micrograph of two perpendicular strain gauges                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 4.8 Testing setup with two moving stages to control the displacement                                                                                                                                                                                                                                                                                                                                                                                            |

| <b>Figure 4.9</b> A simple experiment records the resistance change while the device bends when we applied the displacement in the longitudinal direction                                                                                                                                                                                                                                                                                                              |

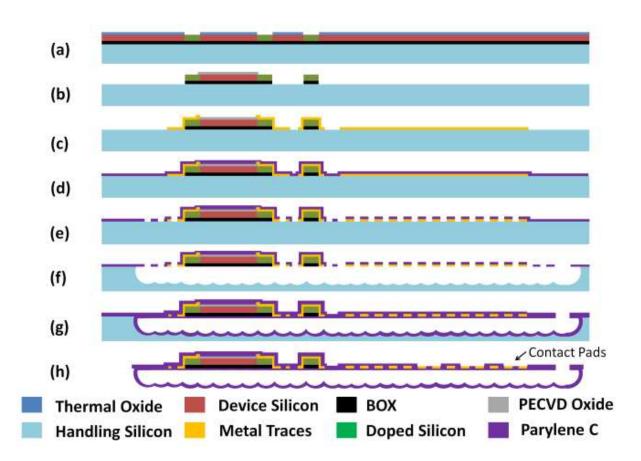

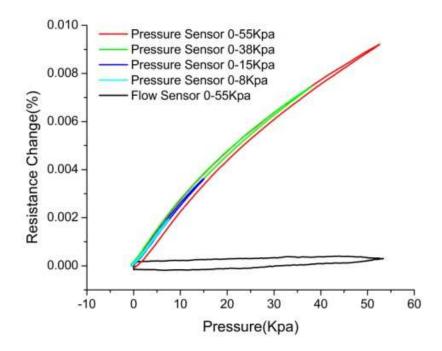

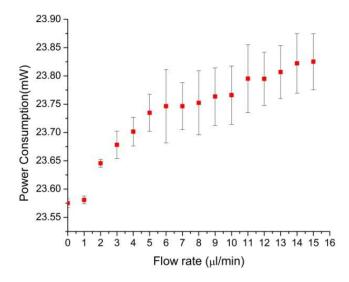

| Figure 5.1 Simplified process flow: (a) Boron diffusion; (b) patterning the Si island on device layer and removing the exposed BOX layer; (c) Al deposition and patterning to form traces and pads;(d) 1st 3 μm parylene deposition; (e) patterning the parylene openings and etching away underneath metal traces; (f) XeF <sub>2</sub> etching to release the devices; (g) 2nd 10 μm parylene deposition; (h) patterning the parylene layer and releasing the device |

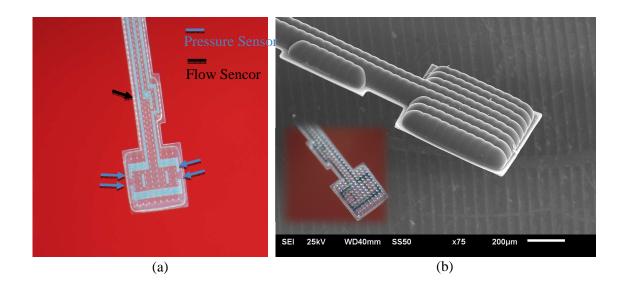

| <b>Figure 5.2</b> (a)Optical image of the fabricated device including both pressure sensor and flow sensor; (b) back side and SEM images of the device; the inset is the optical image of the same device where the front side sensors can be observed through transparent parylene botom layer                                                                                                                                                                        |

| Figure 5.3 Cross-section SEM images of the tail section of the device                                                                                                                                                                                                                                                                                                                                                                                                  |

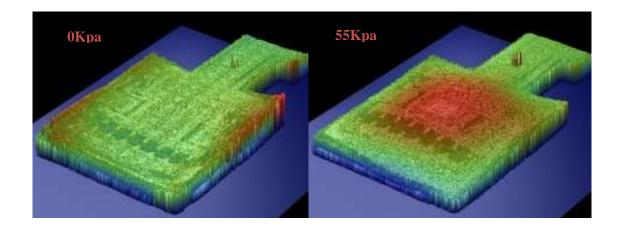

| Figure 5.4 Surface profile of the diaphragm without (left) and with (right) differential pressure applied                                                                                                                                                                                                                                                                                                                                                              |

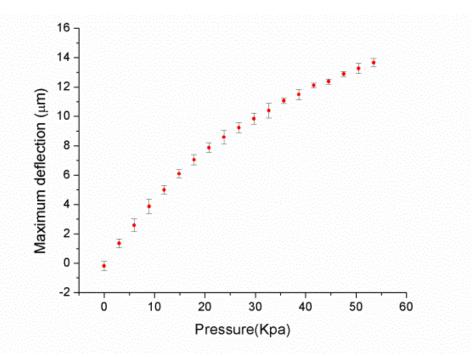

| Figure 5.5 Cross-sectional surface profiles of the pressure sensor diaphragm under different pressures                                                                                                                                                                                                                                                                                                                                                                 |

| <b>Figure 5.6</b> Schematics of our testing setup. The sensing tip of the smart tube device was placed inside the inlet polyimide tubing which enables us to characterize the flow sensor                                                                                                                                                                                                                                                                              |

viii

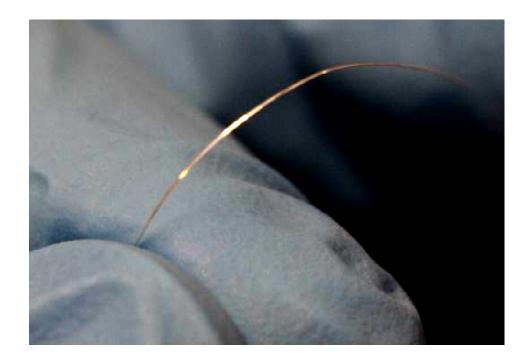

- Figure 6.2 A parylene smart yarn held between fingers and bent to show its flexibility......74

| <b>Figure 6.3</b> Cross-sectional SEM images of our parylene fibers. (a) fiber filled with PDMS; (b)Hollow fiber without PDMS core75                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Figure 6.4</b> (a) SEM image of a kink-free knot made by PDMS filled yarn; (b) SEM image of a kinked knot made by parylene fiber without PDMS core77                                                                                          |

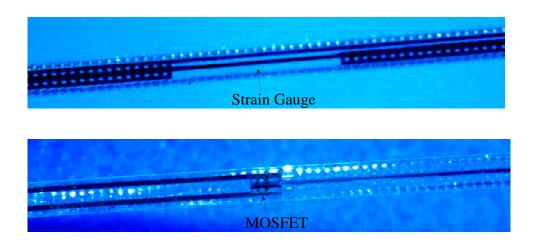

| Figure 6.5 Optical images of a strain gauge and a MOSFET integrated in the parylene yarn.78                                                                                                                                                      |

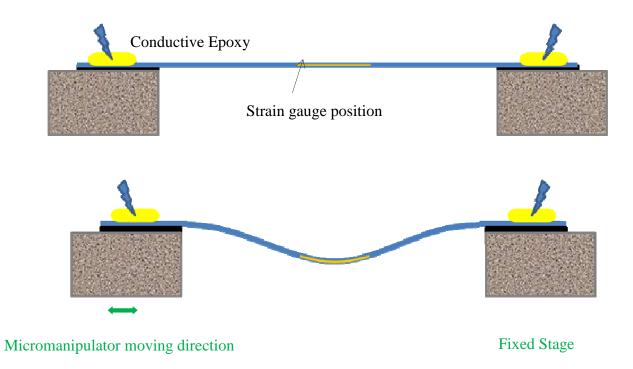

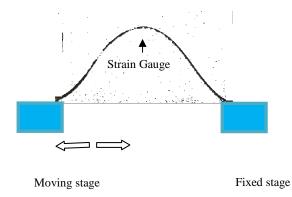

| <b>Figure 6.6</b> Experiment setup: the parylene fiber was secured at two stages with strain gauge positioned at the center. The parylene fiber was flat at initial position. Then the stage moved to the right to a maximum displacement of 3mm |

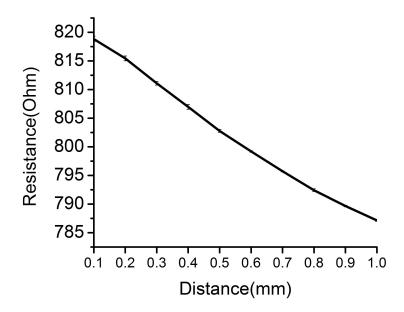

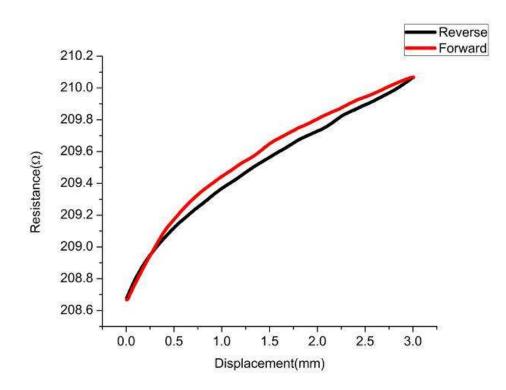

| Figure 6.7 The resistance change of the strain gauge                                                                                                                                                                                             |

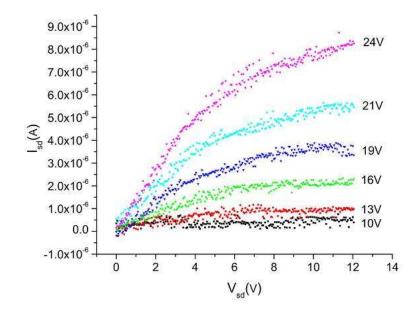

| Figure 6.8 Isd-Vsd curves of one pMOSFET device with different Vsg                                                                                                                                                                               |

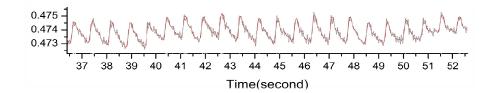

| Figure 6.9    Blood pulse measurement data.    81                                                                                                                                                                                                |

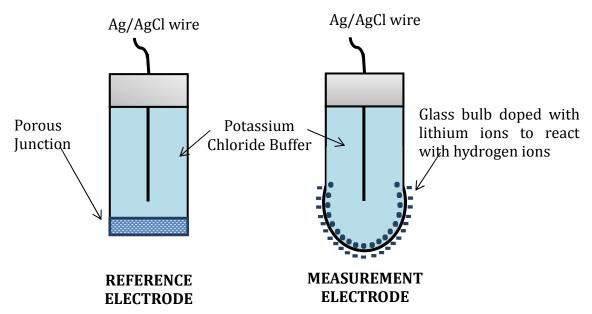

| Figure 6.10 Components of a working pH meter                                                                                                                                                                                                     |

| Figure 6.11 A commercial glass tube pH meter                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                  |

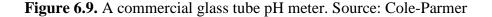

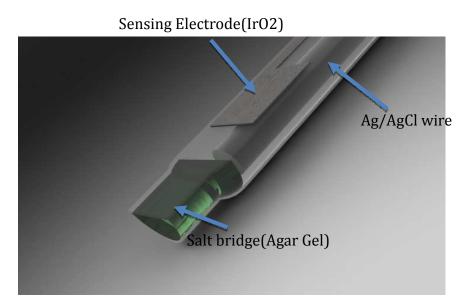

Figure 6.12 Simplified fabrication process: (a) Parylene C coating on a Silicon wafer; (b) Metal deposition to form sensing and contact pads ; (c) patterning the parylene openings; (d) XeF<sub>2</sub> etching to completely undercut the handling wafer and

|             | forms underlying channels; (e) 2nd 10 $\mu$ m parylene deposition to seal the previously opened parylene windows; (f) patterning the parylene layer, open the contact pads and exposing the device inlet and outlet; (g) Backside DRIE etching to release the device from Silicon wafer; (h) Insert the Ag/AgCl wire |   |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|             | and plug one end with Agar gel                                                                                                                                                                                                                                                                                       | 6 |

| Figure 6.13 | 3 Schematic diagram of the proposed device                                                                                                                                                                                                                                                                           | 8 |

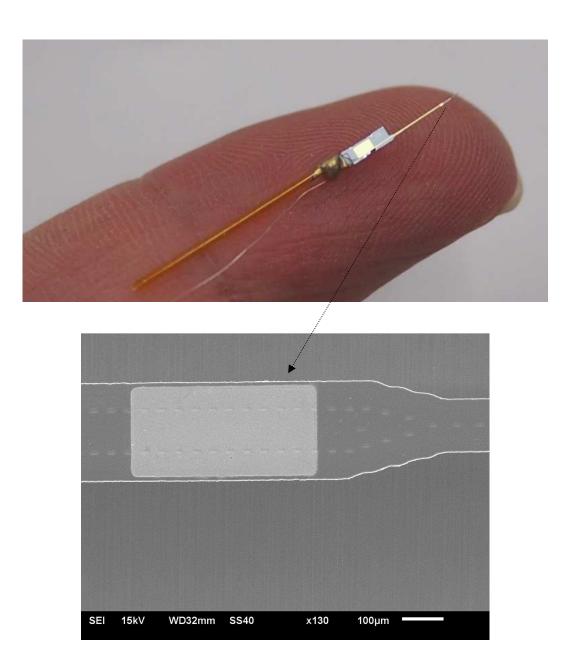

| Figure 6.14 | <b>4</b> (a) Fabricated micro pH sensor place at the finger tip. (b) SEM picture of the exposed Au electrode before $IrO_2$ coating                                                                                                                                                                                  | 9 |

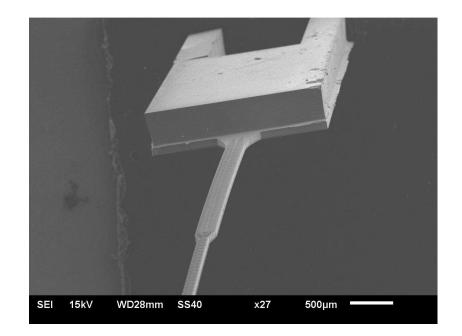

| Figure 6.15 | 5 SEM picture of the micro pH sensor9                                                                                                                                                                                                                                                                                | 0 |

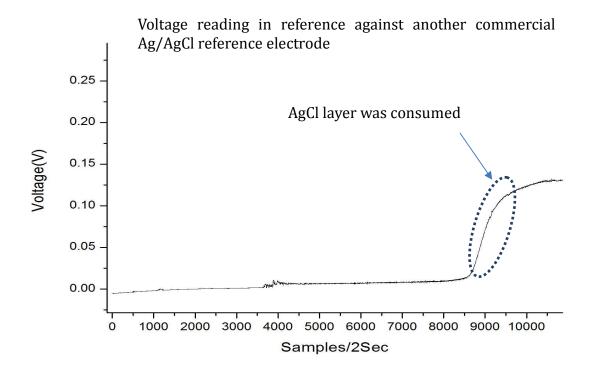

| Figure 6.16 | 6 Potential measurement against another commercial Ag/AgCl electrode                                                                                                                                                                                                                                                 | 1 |

## **CHAPTER 1. Introduction**

#### 1.1 Motivation

MEMS (Micro Electro Mechanical System) devices and CMOS (Complementary Metal Oxide Semiconductor) circuits [1, 2] are traditionally fabricated on rigid substrates with inorganic semiconductor material such as silicon. However, it is highly desirable for functional elements like sensors, actuators or micro fluidic components to be fabricated on flexible substrates for a wide variety of applications. A number of approaches to make flexible sensors or electronics have been developed over the past two decades. The most straightforward approach is the direct fabrication of functional components on a flexible substrate, such as the widely used flexible printed circuitry technology [3] and the thin film transistor (TFT) technology [4-6] on flexible substrates. Various flexible sensors and electronics have been developed as wearable health monitoring devices and medical implants[5]. This direct fabrication of functional elements on flexible substrate has the advantages of simple fabrication process and low cost. Large area flexible sensors or electronics can be fabricated economically using this method. However, due to the flexible substrate, the process temperature is limited and the material properties are not optimized. This temperature limit makes it almost impossible to monolithically integrate CMOS circuits and many MEMS transducers to the flexible substrate.

A flexible skin technology based on silicon island structure has also been demonstrated. The basic structure of the flexible skin is arrays of silicon islands sandwiched

1

by two layers of polymer. The advantage of this technology is its compatibility with MEMS and CMOS since MEMS devices and CMOS circuits can be fabricated on the silicon wafer before the formation of the flexible skin. The minimum bending radius is determined by the size the of the silicon islands. Based on this technology, flexible shear stress sensor skins [7], the integration of CMOS with the flexible skin [8], and intelligent textiles [9], have been demonstrated.

Recently an innovative "transfer printing" method to make flexible electronics has also been demonstrated [10-13]. More specifically, transistors and other devices are fabricated first on SOI (Silicon-on-Insulator) wafers and then released by sacrificial etching and transferred to flexible substrates by a method similar to "printing." Many exciting applications have been demonstrated [14-16]. On the other hand, this transfer printing step is a yieldlimiting step, especially when the device density increases. In addition, the releasing step is generally incompatible with commercial CMOS processes. Therefore, this method cannot fully take advantage of the mainstream CMOS technology.

In order to address the above mentioned drawbacks of existing technologies, alternative methods have been developed in our lab over the last a few years. We proposed a novel technology based on  $XeF_2$  (xenon difluoride) isotropic silicon etching and parylene C conformal coating, which is able to monolithically incorporate high temperature materials and fluidic channels. This technology has been applied to a variety of applications which are discussed in the following chapters.

#### **1.2 Review of flexible electronics**

A common method to make flexible devices is the direct fabrication of components on flexible substrates, such as the widely used flexible printed circuit board (PCB) technology and the thin film transistor (TFT) technology on flexible substrates. Various electronics devices has been developed utilizing the aforementioned technology.

Another popular method to make electronics flexible is direct mounting of ICs (integrated Circuits) on a flexible printed circuit as demonstrated in Figure 1.1. Polyimide, PEEK or transparent conductive plastic films are a few of the materials commonly used as the flexible substrate in electronic industry. Only simple metal traces to interconnect IC components are required to be fabricated on the flexible substrate, leading to very simple fabrication process. This flexible PCB technology significantly reduced the development cost since the technology used to make rigid PCB can be directly applied to make flexible PCB such as metal etching and silver screen printing. Flexible PCB can be found everywhere in our daily lives. For example, it has been widely used in laptop computers as interconnects between motherboard and display. Unlike the conventional rigid PCB, flexible PCB allow the designer to bent and flex the PCB to a certain degree which gives us much needed freedom to integrate electronics into 3D spaces. As consumer electronic devices are getting smaller, flexible PCB becomes a necessity to establish interconnects between modules.

**Figure 1.1**. Flexible PCB inside an Olympus Stylus camera. From: Steve Jurvetson http://flickr.com/photos/44124348109@N01/2265519.

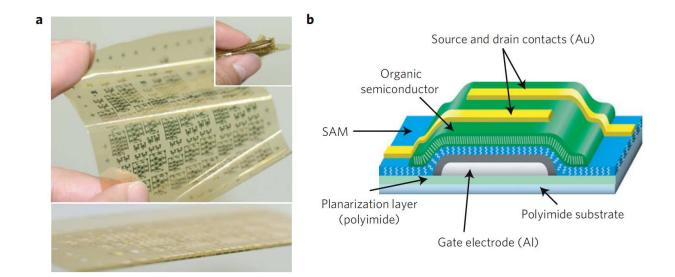

One drawback of the flexible PCB technology is that the bulky packaged IC significantly reduces the overall flexibility of the device. The design of the electronics is limited by the availability and form factor of the IC used. To overcome this drawback, the thin film transistor (TFT) technology has been implemented on flexible substrates. Transistors, the most fundamental elements in building ICs, are traditionally fabricated on rigid substrate like silicon wafers. In order to make transistor on flexible substrate, low temperature semiconductor material has to be developed. For example, in references [17, 18], a flexible organic transistor with extreme bending stability has been developed as demonstrated in Figure 1.2. A flexible polyimide sheet was used as the substrate for the fabrication of transistors in this case. Low process temperature material such as organic self-assembled monolayer (SAM) was chosen to be the gate dielectric layer. Note that only low

temperature material and processes are compatible with this technology. Thanks to the organic material used here, the maximum process temperature is limited to be less than  $100^{\circ}$ C

**Figure 1.2** (a) Photographs of a 12.5  $\mu$ m thick polyimide substrate with functional organic TFTs and organic complementary circuits[17]. The array has an area of 75x75mm<sup>2</sup>. (b), Schematic cross-section of the TFTs.

Without the bulky ICs used in flexible PCB technology, thin film transistor (TFT) technology on flexible substrates makes the device highly flexible. As seen in Figure 1.2, successfully fabricated low-voltage organic transistors, which were placed at the neutral strain position, were folded into a bending radius as small as 100  $\mu$ m without damage to the device. This technology opens a wide range of opportunities for electronic applications that require a high degree of mechanical flexibility. A lot of efforts have been dedicated in the research community to directly integrate low temperature organic materials onto flexible substrate with an intention to reduce the cost and simplify the manufacturing processes.

One drawback is that organic and low temperature materials used in TFT technology normally are not very stable and lack the performance compared with high temperature materials like silicon. Conventional silicon semiconductor devices still perform much better and are required by many applications.

There are technologies developed specifically to integrate silicon devices on flexible substrate. In reference [9], a novel intelligent textile technology based on the integration of silicon flexible skins has been reported.

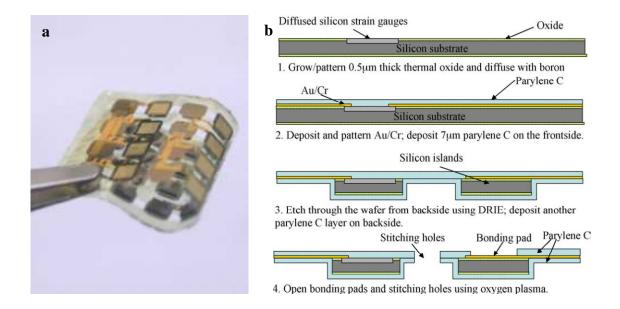

**Figure 1.3.** (a) Picture of a folded skin; (b) Simplified process flow of the flexible skin with integrated strain gauges [9].

As demonstrated in Figure 1.3 (b), simple strain gauges (can be replaced by MEMS devices or ICs) have already been fabricated on the silicon substrate, the first step of the skin development is the fabrication of functional electronic components on a silicon wafer. High

temperature processes are allowed since there are no polymer materials introduced at this stage. Then a polymer layer is coated on the front-side of the wafer. Afterwards, the polymer layer is patterned to expose metal pads. Then, the silicon wafer is thinned down and etched through from the back to form the arrays of silicon islands by deep reactive ion etching (DRIE). Finally, another layer of polymer is coated on the backside to encapsulate silicon islands. The basic structure of the flexible skin is arrays of rigid silicon islands sandwiched by two layers of polymer. A great advantage of this technology is the compatibility with MEMS and IC fabrications. However, due to the large silicon island. In addition, stress concentration between the flexible polymer and rigid silicon has to be addressed to make the whole system more robust.

In addition, other approaches to make flexible electronics without the compromise of high temperature materials have also been developed over the past few years. For instance, functional electronic components are first fabricated on a SOI wafer and then transferred onto a flexible substrate via a stamping method. Additional low temperature processes like the metallization of components are performed directly on the flexible substrate.

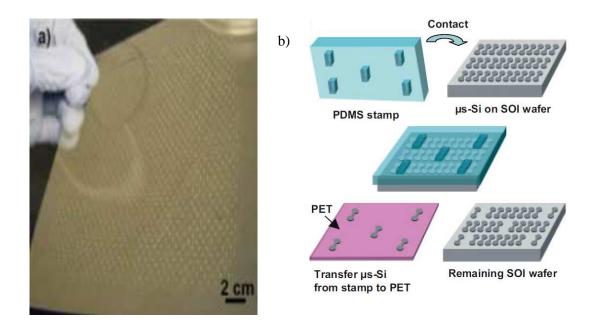

**Figure 1.4.** (a) Optical images of the selective transfer of  $\mu$ s-Si onto a PU/PET sheet; (b)Schematic illustration of selective transfer of us-Si onto PET plastic substrate using patterned hard PDMS [13].

In reference [13], a printing-based approach to make high-performance single-crystal silicon transistors on flexible substrates was reported. As demonstrated in Figure 1.4, a SOI wafer consisting of silicon device layer, buried oxide layer and handling silicon layer were used in the process. The silicon devices ( $\mu$ s-Si) were first fabricated on a SOI wafer by patterning the silicon device layer. A controlled oxide etch was performed to remove the majority of the underling oxide layer. Only a small portion of the oxide layer was left to temporarily hold the  $\mu$ s-Si in position. A specifically designed and patterned PDMS stamp was used to contact the selected  $\mu$ s-Si. Due to the strong adhesion between PDMS and  $\mu$ s-Si,  $\mu$ s-Si can be easily peeled off and transferred to another PET substrate.

Due to the fact that the remaining oxide layer was removed by physical forces, it will destroy part of the  $\mu$ s-Si. Therefore, this risky transfer printing step is a yield-limiting step, especially when the device density increases. In addition, the oxide etching solution (hydrofluoric acid) used in the releasing step makes the process incompatible with commercial CMOS processes. Therefore, this method cannot fully take advantage of the mainstream CMOS technology.

The technology developed in our lab does not suffer from the aforementioned limitations. Both transfer printing method and our method are able to integrate single crystal silicon devices. However, unlike transfer printing method, our method does not need a transfer step and thus has a higher yield. We are able to release the device layer off the handling silicon wafer by an innovative method which will be discussed and presented in the following chapters. Furthermore, our method is post SOI-CMOS compatible, which allows us to utilize commercial foundry and saves a lot of development time and cost.

#### **1.3 Review of the key material and processes**

#### 1.3.1 Parylene C chemical vapor deposition

Parylene also known as poly(p-xylylene) is a polymer commonly used as structure material, moisture and dielectric barriers in MEMS and electronic devices[19-21]. There are many more benefits associated with the the parylene. For example, parylene film exhibits strong chemical resistance and thus is considered as a good barrier for organic and inorganic media, acids and caustic solutions and gases. In addition, parylene's biocompatibility has also been proven and been utilized in many biomedical applications [22-24].

There are three major parylene polymers referred as payrlene C, parylene N and parylene D. Parylene N provides higher dielectric strength and more stable dielectric constant. parylene D will maintain its physical strength and electrical properties at slightly higher temperatures compared with parylene C the most predominant type of parylene. Parylene C is used for almost all types of applications, including our process as well.

|            | Density<br>(g/cm) | Young's modulus<br>(Gpa) | Tensile strength<br>(Mpa) | Dielectric constant<br>(at 1MHz) |

|------------|-------------------|--------------------------|---------------------------|----------------------------------|

| Parylene C | 1.289             | 2.8                      | 68.9                      | 2.95                             |

| Polyimide  | 1.42              | 3.2                      | 70-90                     | 3.5                              |

Table 1.1 Lists of selected properties of parylene C and polyimide

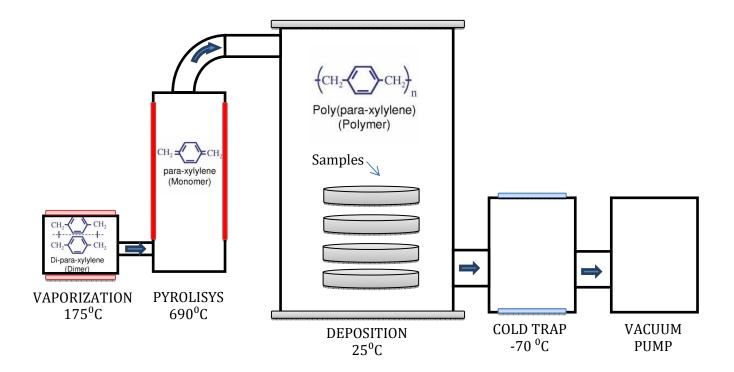

To better understand the physical properties of parylene C, a comparison between polyimide and parylene C used in our process is presented in Table 1.1. Both polyimide and parylene exhibit very similar mechanical properties. In many applications parylene can just simply replace polyimide. One major difference between those two materials is the coating process. Polyimide is normally dissolved in solvent and then applied to the substrate via spin coating. Thickness of the coated film is determined by the spin speed and the viscosity of the dissolved solutions. On the other hand, a process called Chemical Vapor Deposition (CVD) [25] is used to deposit parylene film on the substrate. A simplified block diagram of parylene deposition system is demonstrated in Figure 1.5

Figure 1.5. A common setup flow of chemical vapor deposition of parylene

Parylene coating is a room temperature CVD process. The parylene dimer is first loaded inside the vaporization chamber. The vacuum pump will bring the entire system under vacuum condition. Under the vacuum condition The Dimer begins to vaporize once this vaporization chamber reaches the temperature of 175 °C. The vapor passes through the pyrolysis chamber to undergo a thermal decomposition process and breaks down into a monomer at 690 °C. When the monomer reaches the sample in the deposition chamber at room temperature, it will conformally coat the entire exposed surface and cross-linke to form a parylene film. Excessive monomer will then be trapped by the cold trap to prevent damage to the vacuum pump.

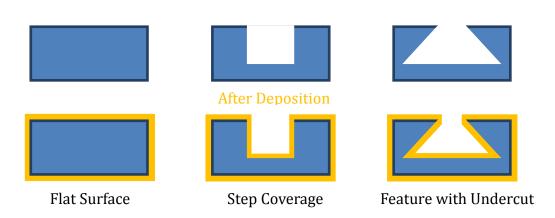

A great benefit of CVD is that the deposition is highly conformal. As schematically illustrated in Figure 1.6, the coating material will get inside a feature with steps and undercut cavities to encapsulate the entire surface. This feature is not feasible using the conventional spin coating process.

#### Figure 1.6. Schematic illustration of conformal CVD coating.

#### 1.3.2 XeF<sub>2</sub> isotropic silicon etching

Another important etching procedure called  $XeF_2$  (Xenon difluoride) [26] isotropic silicon etching has been utilized in our process. This isotropic gaseous etchant for silicon, has been widely used in the semiconductor industry, particularly in the production of MEMS devices [27, 28].

The etching mechanism is actually very simple and easy to implement. First, the  $XeF_2$  molecule dissociates to xenon and fluorine when the gas reaches the surface of silicon. Fluorine then reacts with silicon and forms another gas-phase byproduct. The reaction describing the reaction process is listed below:

$2 \; XeF_2 + Si \longrightarrow 2 \; Xe + SiF_4$

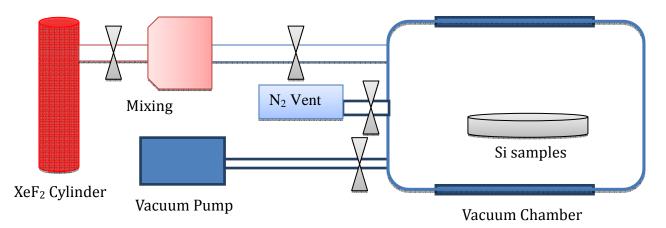

Unlike other plasma etching process, XeF2 has a relatively high etch rate and does not require ion bombardment or external energy sources to etch silicon. A simple illustration of etching apparatus is shown in Figure 1.7.

#### Control Valves

Figure 1.7. Schematic of XeF<sub>2</sub> isotropic silicon etching apparatus.

First, highly concentrated XeF<sub>2</sub> etching gas is contained in a pressurized container. A needle valve is placed between the gas cylinder and mixing chamber which functions as a buffer to prevent gas from coming out too fast. The sample to be etched is then placed inside a vacuum chamber and pumped down to 50 millitorr. N<sub>2</sub> gas is used here to purge the chamber to eliminate any residual moisture. XeF<sub>2</sub> is highly reactive and will react with moisture and produce highly corrosive and dangerous HF as indicated by the formula presented below.

$$2XeF_2 + 2H_2O \rightarrow 4HF + O_2 + 2Xe$$

After the removal of the moisture, the vacuum pump is stopped and leakage is checked before opening the valve after mixing chamber. Due to the nature of the reaction, pressure inside the vacuum chamber will rise up to around 700 millitorr in our particular setup before closure of the valve from the mixing chamber. This practice gives us better control over the

amount of the  $XeF_2$  that gets inside the etching chamber. Vacuum chamber pressure will keep rising up to around 800 millitor before all of the XeF2 gas is consumed. A complete etching loop is complete at this point. Additional loops are repeated to control the amount of the etching.

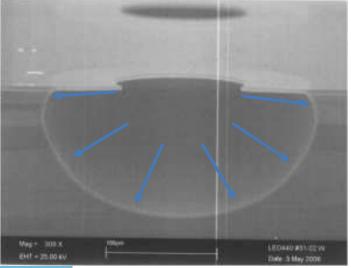

$XeF_2$  silicon etching process is highly selective. A variety of material can be used as masking layer which include but are not limited to photoresist, parylene, metals and silicon dioxide. Another key characteristic of this gas phased etching process is that the process is highly isotropic. As demonstrated in Figure 1.8, huge undercut can be observed after just a few loops of  $XeF_2$  silicon etching.

**Figure 1.8.** Under cut observed after few loops of  $XeF_2$  silicon etching. A circular hole is opened in parylene C layer which functioned as a masking layer.

The amount of the  $XeF_2$  gas that gets inside the etching chamber is fixed between etching loops. The etch rate of  $XeF_2$  is a function of the exposed silicon area. A good way to control the etching process is to unload the sample after a few loops and observe the etching rate under microscope, and then adjust the processing time accordingly.

#### 1.3.3 Deep reactive-ion etching

Another important MEMS fabrication process used in our technology is deep reactive-ion etching (DRIE) [29, 30]. Unlike  $XeF_2$  silicon etching process, DRIE is a highly anisotropic plasma etching process primarily used to sculpture silicon devices. The process can create deep and steep side walled features, typically with very high aspect ratios. This technology has been heavily utilized to develop MEMS devices.

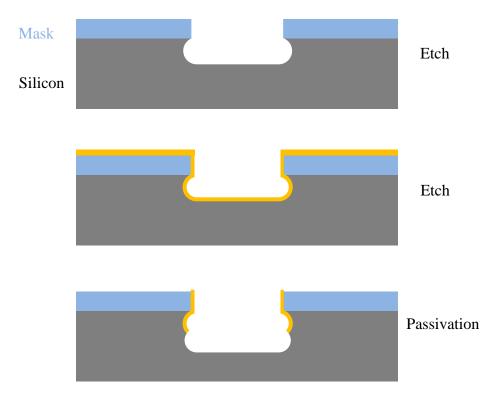

The most common method of DRIE is referred as Bosch process which is a patented process developed by Bosch Inc. Fluorine based chemistries are normally used to etch silicon. However, they all exhibit some degree of isotropy. In order to achieve anisotropic effect and etch nearly vertical walls for high aspect ratio structures, two separate steps are used in Bosch process as demonstrated in Figure 1.9.

First of all,  $SF_6$  plasma etching is performed to isotropically etch exposed the silicon for a short period of time normally less than 10 seconds to prevent the undercut. Then SF6 gas is replaced with C4F8 which will form a Teflon-like substance in plasma and coat the entire chamber and surface. Note that The SF6 does not etch the polymer on the side walls but will attack the coating on the bottom and top surface. The previous etched sidewall is protected from the SF6 isotropic etching. The combination of both the etching step and passivation step makes a very deep vertical structure.

Figure 1.9. A simple demonstration of deep reactive ion etched trench using Bosch process

www.manaraa.com

The figure bellow illustrates that the process will causes ripples or scallops in the side walls due to the nature of the isotropic silicon etching steps utilized.

Figure 1.10. Scallops of a silicon structure created using the Bosch process. Source: Wikimedia

**Figure 1.11.** Different DRIE recipes to create different slope angles[31]. (a) Trench with a positive slope. (b) Trench with a negative slope

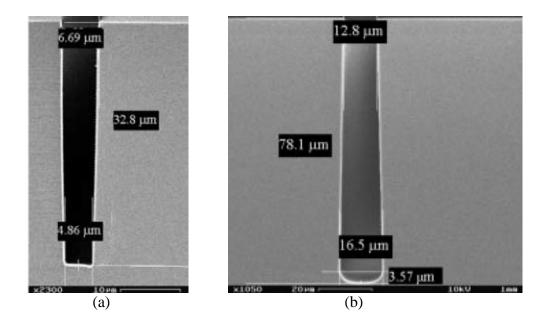

passivation steps. By modifying the ratio between those two steps, different side wall angles can be achieved. As demonstrated in Figure 1.11, both positive and negative slopes can be created in the DRIE process. This technique is utilized in the process of developing our outof-plane parylene microneedle device which is discussed in detail in Chapter 2.

#### **1.4 Dissertation Organization**

In Chapter 2, the technology we developed over the past few years is first implemented in the creation of flexible out-of-plane parylene microneedle arrays [32] that can be individually addressed by integrated flexible micro-channels. These devices enable the delivery of chemicals with controlled temporal and spatial patterns and allow us to study neurotransmitter-based retinal prosthesis.

In addition to the fabrication of micro-fluidic components, other great functionalities can be achieved by integrating otherwise sacrificial silicon wafers to be a part of the device. A hybrid silicon-polymer platform for self-locking and self-deploying origami [33] is demonstrated in Chapter 3.

The ability to incorporate high-temperature materials into flexible substrate is also highly desirable. The technology is further explored in Chapter 4 by adopting the conventional SOI-CMOS processes[34]. High performance and high density CMOS circuits can be first fabricated on SOI wafers, and then can be integrated into flexible substrate. Currently, the best electronics are still made by silicon based CMOS technology. Therefore, it is highly desirable to have a flexible skin technology that is compatible with both MEMS and CMOS processes. Flexible p-channel MOSFETs (Metal-Oxide-Semiconductor Field-Effect-Transistors) and high performance silicon strain gauges were successfully fabricated and tested.

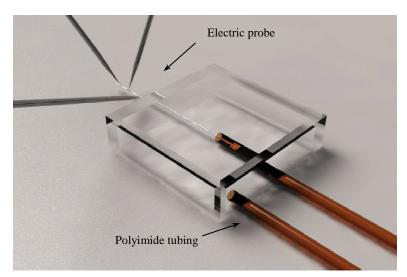

In Chapter 5, the development of a smart tube[35] with integrated pressure and flow sensor is presented. The ability to monolithically incorporate electronic components and micro-fluidic structure is highly desirable. This integration is able to bring additional functionality, higher performance, simplified packaging, reduced size/weight and cost to the flexible sensors.

Finally in Chapter 6, some of the additional examples like the smart yarn device and micro pH sensor developed by this technology are presented. A few important future applications are also discussed.

## **CHAPTER 2.** Parylene microtube arrays

#### 2.1 Introduction

The technology discussed in this thesis is first implemented in making flexible parylene microneedle arrays with integrated micro channels for retinal prosthesis study. Many groups have been working toward the development of retinal prosthesis systems that can provide artificial vision to the blind [36-38]. An effective retinal prosthesis would improve the lives of hundreds of thousands of patients with Retinitis Pigmentosa (RP) or millions of blind patients with advanced Age-Related Macular Degeneration (ARMD), depending on its effectiveness. Designs for these prosthetic devices have been based upon the success of electrical stimulation in the cochlear implant. Prostheses based on electrical stimulation of the retina have been under development over the past two-decades as well. In fact, vision is our greatest bandwidth sensory input which requires prostheses to have a neural interface with high spatial and temporal resolution. Testing in acute human studies has demonstrated limited success in providing useful vision. Retinal implant based on electrical stimulation has limitations such as electrode corrosion, water hydrolysis, and generation of toxic radicals due to the large stimulation current. The more naturalistic chemical stimulation is able to effectively address these limitations. This chapter describes the development of parylene microneedle arrays that can be individually addressed by integrated microchannels for neurotransmitter-based retinal prosthesis.

Microneedles can be classified as in-plane or out-of-plane, and solid or hollow. For retinal prosthesis, out-of-plane hollow microneedles are required. A variety of out-of-plane hollow microneedle arrays have already been developed for drug/chemical delivery and other applications. Chun et al. developed  $SiO_2$  microcapillary arrays for the injection of DNA into cells by growing thermal oxide in deep holes etched by DRIE [39]. Hollow silicon microneedles were also developed by Stoeber and Liepmann using a combination of DRIE and isotropic etching [40]. Gardenier et al. developed hollow silicon microneedles with sharp beveled tips using a process combining DRIE, conformal thin film deposition and anisotropic wet etching [41]. In order to address the potential problem of being clogged during the insertion of needles, Griss and Stemme developed hollow out-of-plane silicon microneedles with openings in the shaft instead of at the tip [42]. Kim et al. reported hollow metal microneedle arrays based on backside exposure of SU-8 and electroplating [43]. Hollow metal microneedles have been developed using laser-micromachined polymer mold [44]. Zhu et al. reported another method of fabricating hollow metal microneedles using PMMA molds formed by silica needle template [45]. Hollow microneedles with sharp beveled tips have also been developed using the LIGA technique by taking advantage of its capability of fabricating high-aspect ratio structures [46, 47]. Fluid access to the out-ofplane microneedles is usually made from the back of the wafer by forming a drug reservoir using a wafer bonding method. Consequently, these microneedles are not individually addressable. For retinal prosthesis, however, the microneedles have to be individually addressed due to the requirement of spatial resolution.

Individually addressable out-of -plane microneedle has been developed in our lab as described in the following section. DRIE high aspect ratio silicon etching process is used here to form the molds of the needle arrays. XeF<sub>2</sub> isotropic silicon etching process is employed here to form the accessing microfluidic channels to the needles. Another key process used here is conformal parylene C coating. Parylene C polymer will conformally deposit on the walls of the holes and trenches etched by DRIE and XeF2 forming hollow needles and fluidic channels.

#### 2.2 Design and fabrication

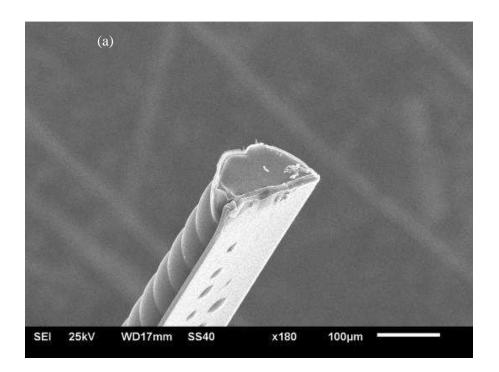

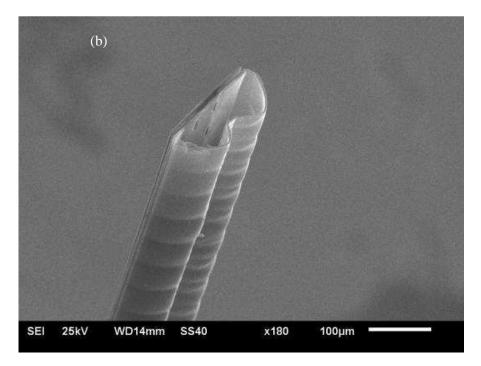

The fabrication was carried out on double-side polished 350 $\mu$ m thick silicon wafers. The thickness of the wafer will determine the overall height of the microneedles. First, a 4  $\mu$ m parylene C layer was deposited on the front side of wafer using SCS PDS2010 coating system. Due to the nature of parylene C coating, both side of the wafer were coated with parylene C. Back side of the wafer went through O<sub>2</sub> plasma to remove the deposited parylene and expose the silicon layer. Next, through-silicon vias of 35  $\mu$ m in diameter were formed by DRIE from the backside of wafer as shown in Figure 2.1(a). Note that the recipe of DRIE has been modified to create a slightly slanted side wall to give the vias pointy shape. Those vias will function as a shape mold to make hollow needles. After the backside etching, 200 nm Al layer was evaporated on the frontside after treating the parylene C layer with a mild O<sub>2</sub> plasma to improve the adhesion. This Al layer was then patterned and subsequently used as an O<sub>2</sub> plasma mask to open 8- $\mu$ m wide windows on the parylene layer as shown in Figure 2.1(b). In the next step, XeF<sub>2</sub>, an isotropic gas phase silicon etchant, was used to form

trenches in the silicon substrate through the windows opened in the parylene layer. The trenches created have an undercut of approximate 25  $\mu$ m from the parylene openings. Note that the trenches were connected with the through-silicon vias as seen in step (c). Then the parylene microchannels were formed and sealed by depositing another 10  $\mu$ m thick parylene C layer.

**Figure 2.1.** The fabrication process of the microneedles with integrated microchannels(a) deposit a parylene C layer; etch through-silicon vias from the backside of the wafer using DRIE; (b) pattern the parylene layer; (c) etch the silicon substrate using XeF<sub>2</sub>; (d) coat a thick parylene layer to seal the channel; (e) pattern the frontside parylene; (f) DRIE from the backside of the wafer using Al mask; (g) remove Al mask and continue DRIE to release Parylene cable. Out-of-plane microneedles also emerged.

The parylene deposition is a very conformal process. Therefore, parylene layer was able to deposit on the inside surfaces of the trenches, forming sealed parylene channels [48]. The cross-sectional view of the sealed parylene channel is demonstrated in step (d). Simultaneously, hollow microneedles were formed by the parylene film deposited inside the through-silicon vias (step (c)). The frontside parylene layer is then patterned with a thick photoresist (AZ4620) mask and the parylene is etched via  $O_2$  plasma as shown in step (e). Next, as shown in step (f), DRIE was carried out on the backside using an aluminum mask to selectively thin down the wafer. When the remaining wafer thickness reached about 100 µm, the aluminum mask was stripped away. Then DRIE continued on the backside until the parylene channels were exposed. Simultaneously, because the etch rate of payrlene in DRIE is much slower compared with that of silicon, parylene microneedles embedded in silicon emerged and protruded above the silicon surface. Note that the height of needles protruding above the silicon surface can be increased by additional DRIE etching.

#### 2.3 Results and discussion

#### 2.3.1 Fabricated device

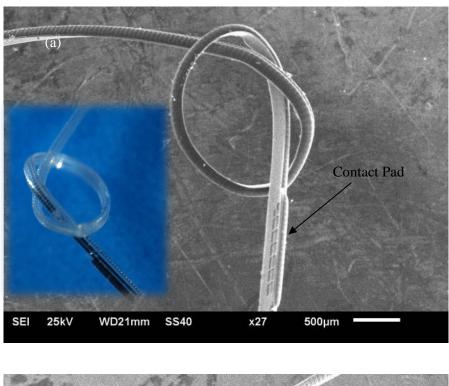

Figure 2.2 (a) shows a fabricated mcironeedle device with flexible parylene cable. The overall length of this device is about 20 mm. It consists of two silicon islands connected by a flexible parylene cable embedded with microchannels. The left silicon island carries 4 slender beams which facilitate the coupling of external tubings to on-chip microchannels. Figure 2.2 (b) shows the SEM image of a microchannel inlet on the tip of the coupling beam. As shown in Figure 2.2(c), the right small silicon island hosts a 2x2 microneedle array. These parylene microneedles are about 80  $\mu$ m high, and with an outer diameter of 35  $\mu$ m and an inner diameter of 15  $\mu$ m. It is worth noting that the height of microneedles can be adjusted by controlling the DRIE loops in step (f) and (g). The in-plane parylene microneedles at the bottom surface of the silicon island. Each microneedle can be individually addressed by the inlet ports on the left silicon island.

**Figure 2.2.** (a) A Polyimide Tubing coupled microneedle device with 1.5 cm long flexible parylene cable. Epoxy is used to seal the coupling interface; (b) SEM image of the microchannel inlet port on one coupling beam; (c) SEM image of the small silicon island on the tip of the parylene cable; (d) cross-sectional view of a micrchannel embedded in the parylene cable; (e) magnified view of the 2x2 microneedle array on the small silicon island.

The cross-sectional SEM image of a parylene channel embedded in the parylene cable is shown in Figure 2.2(d). Note that this channel was formed using two columns of openings. The groves resulting from the sealing of the two columns of openings can be clearly observed. The marks due to the isotropic XeF2 etching from adjacent openings can also be seen from the parylene channel walls. This device enables in-vivo animal study. Namely, the small silicon island containing the microneedle array can be implanted into the eye of an animal (e.g., cat or monkey). Neurotransmitters such as glutamate can be ejected to retina through the flexible parylene channels.

Rigid needle arrays have also been developed for in-vitro retinal stimulation study as seen in Figure 2.3. In order to improve the robustness of our device, rigid devices integrated with  $4\times4$  microneedle arrays have been fabricated. The  $4\times4$  microneedle array locates in the center of the device and covers an area of 500 µm × 500 µm. The dimensions of these needles are same as those on flexible devices. The  $4\times4$  microneedles can be individually addressed by 16 microchannels whose inlets are distributed along the 4 edges of the 1.2 cm × 1.2 cm square silicon chip.

**Figure 2.3.** (a) Photograph of a rigid microneedle device. The device carries 16 slender beams, each of which contains one microchannel inlet. (b) SEM image of the 4x4 microneedle array located in the center of the chip, which can be addressable by 16 microchannels.

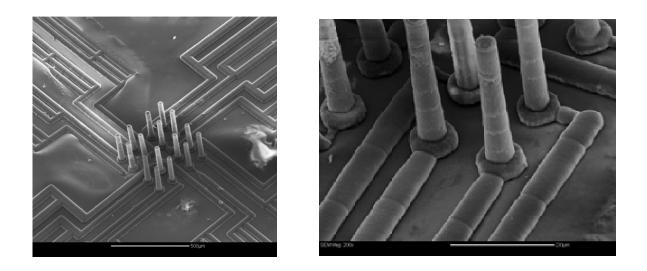

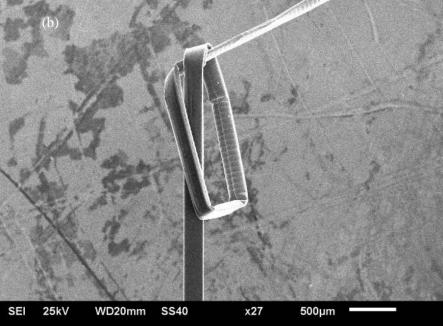

To investigate the connection between the needles and channels, silicon of the rigid device was completely dissolved by TMAH (Tetramethylammonium hydroxide). It has been demonstrated previously that parylene C is not attacked by TMAH [49]. Figure 2.4 (a) shows the SEM image of the resulting pure parylene device. The tapered shape of microneedles was formed by adjusting the parameter of DRIE during the etching of through-silicon vias. The parylene microchannels previously embedded in the silicon substrate now can be clearly observed. It can also be observed how the out-of-plane parylene microneedles are connected to in-plane parylene microchannels in the magnified view shown in Figure 2.4 (b). Note that XeF<sub>2</sub> at step (c) also attacked through-silicon vias. However, XeF<sub>2</sub> only enlarged the bottom part of the vias as evidenced by the donut structures at the bottom of microneedles shown in Figure 2.4. (b).

(a) (b) **Figure 2.4.** (a) SEM image of the pure parylene device by dissolving away silicon. (b) Magnified SEM image of the connection between out-of-plane microneedles and in-plane channels

#### 2.3.2. Fluidic injection test

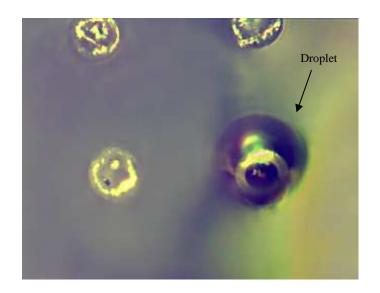

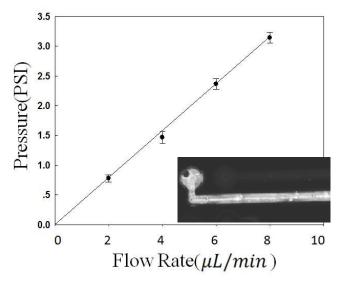

In order to test the connection between the microneedle and microchannel, fluorescent dyes were injected to one microchannel under a pressure up to 8 psi. The resulting fluorescent image is shown in the inset of Figure 2.5(b). The connection between the circular area, which is the bottom of the microneedle, and the in-plane microchannel can be clearly observed. The flow rate of a microchannel was measured using DI (deionized) water. Polyimide tubing (with an inner diameter of 620 microns) was coupled to the microchannel and then sealed using epoxy as demonstrated in Figure 2.2 (a). A programmable syringe pump and a pressure sensor were used for dispensing liquid and measuring pressure. The flow rate as a function of pressure applied was measured and plotted in Figure 2.5(b). Figure 2.5(a) shows the micrograph of a water droplet emerged from one of the microneedles.

(a)

(b)

**Figure 2.5.** (a) Optical micrograph showing a water droplet emerging from one microneedle. (b) The measured relationship between the applied pressure and flow rate. The inset is a fluorescent image of the microchannel and donut structure at the bottom of the microneedle (the channel was filled with fluorescent solution).

#### 2.3.3. Preliminary in-vitro retina test

In addition to the fluidic tests done in our lab, the fabricated device was sent to our collaborator Dr. Paul Finlayson for a preliminary in-vitro retina test. A retina tissue was removed from a rat and cultured in a small container for testing. Then our microneedle device was placed in close contact with the retinal tissue along with a small electrode placed next to the needle outlet for neural activity monitoring. As shown in Figure 2.6., chemical based neurotransmitter was delivered to the retinal tissue via a 10 PSI pressure pulse. Retinal tissue's prompt neural response can be clearly observed in the form of electrical spikes.

**Figure 2.6.** Neurotransmitter ejection pressure pulse and the resulting neural spikes. Source: Dr. Finlayson.

### 2.4 Summary

We demonstrated a novel microfabrication technology of out-of-plane individually addressable microneedle arrays with integrated parylene microchannels. Two different types of devices, rigid devices for in-vitro retina stimulation study and flexible devices integrated with parylene cables for in-vivo study have been developed. The fabrication takes advantage of the conformal coating of parylene. The molds of parylene, including the trenches and through-silicon vias, are formed by XeF<sub>2</sub> etching and DRIE, respectively. Microneedles and microchannels are formed by coating parylene conformally inside the vias and trenches. The functionality of the device has been demonstrated by ejecting water through microneedles. A simple perfusion chamber is being built on the top of the rigid chip for the in-vitro retinal stimulation study. The flexible device allows in-vivo study by implanting the small silicon island containing the microneedle array into the eye of animal (cat or monkey) and injecting neurotransmitters such as glutamate through the flexible parylene channels. Our device enables the delivery of drugs to the desired sites with high spatial resolution.

# CHAPTER 3. Hybrid silicon-polymer platform for self-locking and self-deploying origami

#### 3.1Introduction

Origami, traditionally the art of paper folding, has been applied to a variety of engineering applications based on its principle of creating three-dimensional (3D) structures from two-dimensional (2D) sheets through a high degree of folding along the creases. The applications of origami ranges from space exploration (e.g., a foldable telescope lens[50]), to automotive safety (e.g., airbags), and biomedical devices (e.g., heart stent[51]). Materials like shape memory alloy [52] in forms of coil and thick flat plates has been developed to achieve effective bending motion for origami structure. Those origami devices are fabricated by precision machining or laser micromachining [53]. More traditional microfabrication methods such as photolithography have also been used as well [54-56]. The employment of microfabrication will potentially allow the monolithic integration of electronics and MEMS sensors with origami. We developed an origami platform based on microfabricated silicon island arrays. This Silicon-polymer hybrid platform takes the advantages of the excellent rigidity of silicon substrate and combines the flexibility of polymer technology to make flexible devices. Not only it renders the whole device reasonably flexible, it also can be employed to achieve functions like actuation[57]. The technology presented in the previous chapter has been adopted to develop our origami platform. CMOS electronics and MEMS devices can be first fabricated on the silicon wafers [7, 8, 58]. Then low-temperature

processes are carried out to form silicon island arrays and the parylene balloon creases. Such an origami platform, with its capability to integrate CMOS circuits and MEMS sensors, selflock and self-deploy, will be of great interest to the fabrication of some 3D devices.

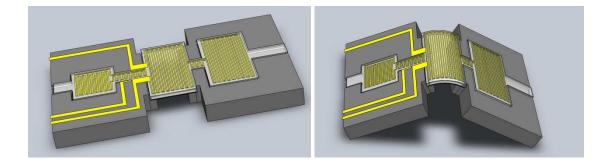

The proposed origami device and operation principle of self-locking and selfdeployment is schematically illustrated in Figure 3.1. The discrete silicon islands are connected by a parylene balloon at the creases integrated with a metal heater and filled with paraffin wax. Of cause, other materials exhibits phase change at low temperature can be used as well. Paraffin wax was chosen in this experiment. The paraffin wax can be melted by applying electric current to the heater and return to the solid state by turning off the heater. To fold the origami, the wax is melted first, making the balloon flexible. Then the device is folded by external forces. While the device is kept in the folded state, the heater is turned off. The wax solidifies and the origami is locked in the folded state. For the deployment, the heater is turned on to melt the wax to the liquid state. Thus the folded origami can return to its original flat state when the heater is on due to the elastic restoring force of the parylene balloon.

**Figure 3.1.** Schematic of the silicon island origami with a parylene balloon crease for self-locking and self-deploying functions.

#### 3.2 Design and fabrication

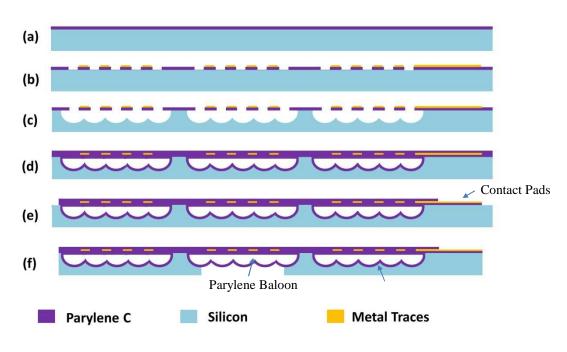

The simplified fabrication is illustrated in Figure 3.2. A 500 µm thick silicon wafer was used for the fabrication. First the wafer was thoroughly cleaned and deposited with 3  $\mu$ m thick parylene C layer as shown in Figure 3.2(a). Then as show in Figure 3.2(b), a layer of 25/200 nm Ti/Au layer was deposited and patterned to form the micro heaters, bonding pads and corresponding connection traces. Ti was used here to improve the adhesion between parylene C and Au. Next, an array of 8  $\mu$ m  $\times$  20  $\mu$ m parylene openings was etched via O<sub>2</sub> In the next step, through the parylene C windows, the silicon substrate was plasma. selectively etched by isotropic gas-phase etchant  $XeF_2$  as illustrated in Figure 3.2(c). The depth of the undercut was measured to be 50  $\mu$ m in this case. Larger depth can be achieved by increasing the exposure time to  $XeF_2$  or using DRIE to deepen the openings before XeF2 etching. These cavities define the shape of parylene balloons. Another thicker layer of parylene C film was conformally deposited on the bottom and side walls of the cavities as shown in Figure 3.2(d). This parylene C layer simultaneously sealed the perforated top parylene C film and encapsulated the metal heaters. Oxygen plasma was then used to pattern the parylene layer to define individual devices and expose the contact pads as shown in Figure 3.2(e). Finally the backside of the wafer were patterned and etched via DRIE to form the silicon islands and release the flexible parylene balloon creases as demonstrated in Figure 3.2(f). Note that the balloons extend into the silicon islands. This actually provides cushions between the metal traces and the rigid edge of silicon islands, significantly reducing stress concentration as demonstrated in our previous work [59].

Additional Reservoir

Figure 3.2. Simplified fabrication process of the Origami device.

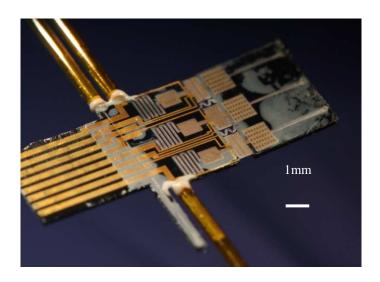

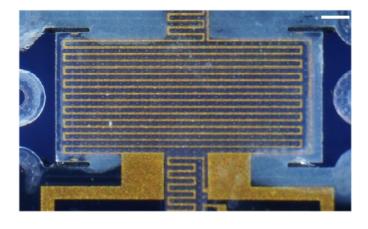

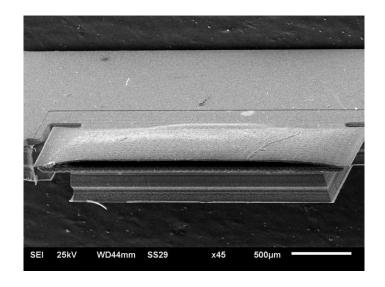

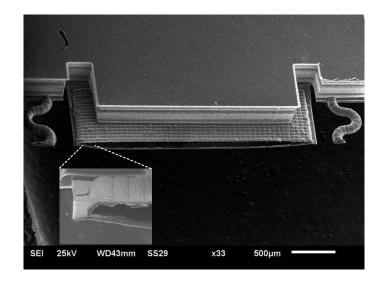

Figure 3.3(a) is a micrograph of a fabricated device. Since the present work is to demonstrate the self-locking and self-deploying features, the testing device only contains two silicon islands that are connected by 3 parallel parylene balloons. The integrated heaters can be accessed by the bonding pads placed on the left side. Polyimide tubes were glued for the injection of melted wax. The detail of the integrated heater can be observed in Figure 3.3(b). More details of the parylene balloon can be found in the front side and back side SEM images shown in Figure 3.4. Note that the parylene balloon was cut in the middle using a razor blade in order to observe the cross section.

40

(a)

(b)

**Figure 3.3.** (a) Front side micrograph of an actual fabricated micro hinge structure with three individual Paraffin wax filled parylene balloon hinge; (b) micrograph of the metal heater integrated on the parylene balloon.

(a)

(b)

**Figure 3.4.** (a) Front side and (b) backside SEM images of a parylene balloon cut to show its cross section. The inset shows the enlarged view of the balloon.

#### 3.3 Device testing and characterization

The balloons need to be filled with paraffin wax for the self-locking and selfdeploying functions. This was achieved by placing the whole device on a hotplate with the temperature set at 60 °C, above the melting point of the paraffin wax (327212, Sigma-Aldrich). The melted wax was then simply injected via a syringe. The filling was stopped once excessive wax was observed on the outlet of the channel.

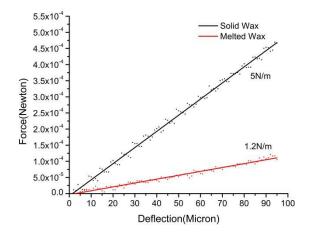

42